# **Hex EIA-485 Transceiver** with Three-State Outputs

The Motorola MC34058/9 Hex Transceiver is composed of six driver/receiver combinations designed to comply with the EIA–485 standard. Features include three–state outputs, thermal shutdown for each driver, and current limiting in both directions. This device also complies with EIA–422 and CCITT Recommendations V.11 and X.27.

The devices are optimized for balanced multipoint bus transmission at rates to 20 MBPS (MC34059). The driver outputs/receiver inputs feature a wide common mode voltage range, allowing for their use in noisy environments. The current limit and thermal shutdown features protect the devices from line fault conditions.

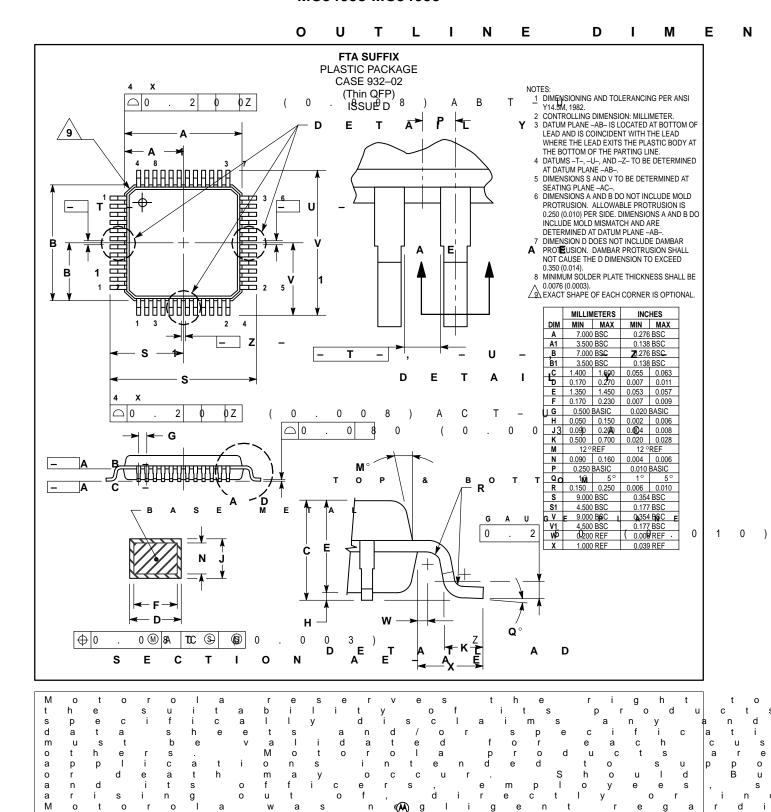

The MC34058/9 is available in a space saving 7.0 mm 48 lead surface mount quad package designed for optimal heat dissipation.

- Meets EIA-485 Standard for Party Line Operation

- Meets EIA–422A and CCITT Recommendations V.11 and X.27

- Operating Ambient Temperature: 0°C to +70°C

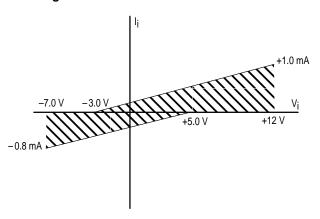

- Common Mode Driver Output/Receiver Input Range: -7.0 to +12 V

- Positive and Negative Current Limiting

- Transmission Rates to 14 MBPS (MC34058) and 20 MBPS (MC34059)

- Driver Thermal Shutdown at 150°C Junction Temperature

- Thermal Shutdown Active Low Output

- Single +5.0 V Supply, ±10%

- Low Supply Current

- Compact 7.0 mm 48 Lead TQFP Plastic Package

# HEX EIA-485 TRANSCEIVER with THREE-STATE OUTPUTS

SEMICONDUCTOR TECHNICAL DATA

#### **ORDERING INFORMATION**

| Device     | Operating Temperature Range                    | Package |  |

|------------|------------------------------------------------|---------|--|

| MC34058FTA | T. 00 to 1700C                                 | TQFP-48 |  |

| MC34059FTA | $T_A = 0^\circ \text{ to } +70^\circ \text{C}$ | TQFP-46 |  |

#### **MAXIMUM RATINGS**

| Rating                                                                    | Symbol           | Value         | Unit |

|---------------------------------------------------------------------------|------------------|---------------|------|

| Power Supply Voltage                                                      | Vcc              | -0.5, 7.0     | Vdc  |

| Input Voltage (Driver Data, Enables)                                      | V <sub>in</sub>  | 7.0           | Vdc  |

| Applied Driver Output Voltage When in Three–State Condition (VCC = 5.0 V) | VZ               | -10, 14       | Vdc  |

| Applied Driver Output Voltage When V <sub>CC</sub> = 0 V                  | ٧x               | ±14           | Vdc  |

| Output Current                                                            | lo               | Self Limiting | _    |

| Storage Temperature                                                       | T <sub>stg</sub> | -65, 150      | °C   |

**NOTE:** Devices should not be operated at these limits. The "Recommended Operating Conditions" provides for actual device operation.

## RECOMMENDED OPERATING CONDITIONS (All limits are not necessarily functional concurrently.)

| Characteristic                                                                                 | Symbol          | Min  | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------|-----------------|------|-----|-----|------|

| Power Supply Voltage                                                                           | Vcc             | 4.5  | 5.0 | 5.5 | Vdc  |

| Input Voltage (All Inputs Except Receiver Inputs)                                              | V <sub>in</sub> | 0    | _   | Vcc | Vdc  |

| Driver Output Voltage in Three–State Condition, Receiver Inputs, or When V <sub>CC</sub> = 0 V | VСМ             | -7.0 | -   | 12  | Vdc  |

| Driver Output Current (Normal Data Transmission)                                               | IO              | -60  | _   | 60  | mA   |

| Operating Ambient Temperature                                                                  | TA              | 0    | _   | 70  | °C   |

# **ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ , $V_{CC} = 5.0 \text{ V} \pm 10\%$ )

| Characteristic                                  |                                                                                  | Symbol              | Min  | Тур  | Max | Unit |  |

|-------------------------------------------------|----------------------------------------------------------------------------------|---------------------|------|------|-----|------|--|

| DRIVER CHARACTERISTICS                          | DRIVER CHARACTERISTICS                                                           |                     |      |      |     |      |  |

| Output Voltage                                  |                                                                                  |                     |      |      |     |      |  |

| Single Ended, I <sub>O</sub> = 0                |                                                                                  | Vo                  | 0    | _    | Vcc | Vdc  |  |

| Differential, Open Circuit (I <sub>O</sub> = 0) |                                                                                  | V <sub>OD1</sub>    | 1.5  | _    | _   | Vdc  |  |

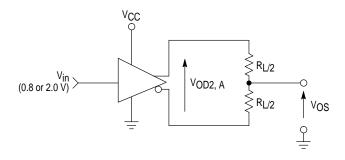

| Differential, $R_L = 54 \Omega$                 |                                                                                  | IV <sub>OD2</sub> I | 1.5  | _    | _   | Vdc  |  |

| Change in Differential Voltage (No              | ote 1), $R_L = 54 \Omega$                                                        | ∆V <sub>OD2</sub>   | _    | -    | 200 | mVdc |  |

| Differential, $R_L = 100 \Omega$                |                                                                                  | ∆V <sub>OD2</sub> A | 2.0  | _    | _   | Vdc  |  |

| Change in Differential Voltage (No              |                                                                                  | IVOD2Al             | _    | -    | 200 | mVdc |  |

| Common Mode Voltage, R <sub>L</sub> = 54        |                                                                                  | Vосм                | _    | _    | 3.0 | Vdc  |  |

| Common Mode Voltage Change,                     | $R_L = 54 \Omega$                                                                | I∆VOCMI             | -    | _    | 200 | mVdc |  |

| Output Current (Each Output)                    |                                                                                  |                     |      |      |     | mA   |  |

| Short Circuit Current, −7.0 V ≤ V <sub>C</sub>  | Short Circuit Current, $-7.0 \text{ V} \le \text{V}_{\text{O}} \le 12 \text{ V}$ |                     |      | _    | 250 |      |  |

| Driver Data Inputs                              |                                                                                  |                     |      |      |     | Vdc  |  |

| Low Level Voltage                               |                                                                                  | VILD                | _    | -    | 0.8 |      |  |

| High Level Voltage                              |                                                                                  | VIHD                | 2.0  | -    | _   |      |  |

| Clamp Voltage (I <sub>in</sub> = −18 mA)        |                                                                                  | VIKD                | -1.5 | _    | _   |      |  |

| Thermal Shutdown Junction Temperature           |                                                                                  | T <sub>JTS</sub>    | -    | 150  | -   | °C   |  |

| RECEIVER CHARACTERISTICS                        |                                                                                  |                     |      |      |     |      |  |

| Input Threshold                                 | R <sub>O</sub> = High                                                            | V <sub>th</sub>     | _    | _    | 200 | mVdc |  |

|                                                 | R <sub>O</sub> = Low                                                             |                     | -200 | _    | _   |      |  |

| Input Loading (Driver Disabled)                 |                                                                                  |                     | _    | 0.36 | 1.0 | U.L. |  |

| Hysteresis                                      |                                                                                  | VH                  | -    | 100  | -   | mV   |  |

| Output Voltage                                  | High ( $I_{OH} = -400  \mu A$ )                                                  | VOHR                | 2.4  | _    | _   | Vdc  |  |

|                                                 | Low ( $I_{OL} = 4.0 \text{ mA}$ )                                                | VOLR                |      | _    | 0.4 |      |  |

| Output Short Circuit Current                    |                                                                                  | IOSR                | _    | 45   | 85  | mA   |  |

| Output Leakage Current When in Three–State Mode |                                                                                  | IOLKR               | _    | _    | 20  | μΑ   |  |

NOTE: 1. Input switched from low to high.

**ELECTRICAL CHARACTERISTICS (continued)** ( $T_A = 25^{\circ}C$ ,  $V_{CC} = 5.0 \text{ V} \pm 10\%$ )

| Characteristic                                                                                                                                                                                                     | Symbol                                                                                                               | Min              | Тур                  | Max                                    | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------|----------------------|----------------------------------------|------|

| MISCELLANEOUS                                                                                                                                                                                                      |                                                                                                                      | •                | •                    | •                                      | •    |

| Enable Inputs Low Level Voltage High Level Voltage Clamp Voltage (I <sub>in</sub> = -18 mA)                                                                                                                        | VILE<br>VIHE<br>VIKE                                                                                                 | 0<br>2.0<br>–1.5 | _<br>_<br>_          | 0.8<br>VCC<br>-                        | Vdc  |

| Power Supply Current (Total Package, All Outputs Open, Enabled or Disabled)                                                                                                                                        | ICC                                                                                                                  | -                | 18                   | 28                                     | mA   |

| Thermal Shutdown Output Voltage High Low                                                                                                                                                                           | VOHT<br>VOLT                                                                                                         | 2.4<br>0         | -<br>-               | _<br>0.8                               | Vdc  |

| TIMING CHARACTERISTICS – DRIVER                                                                                                                                                                                    |                                                                                                                      |                  |                      |                                        |      |

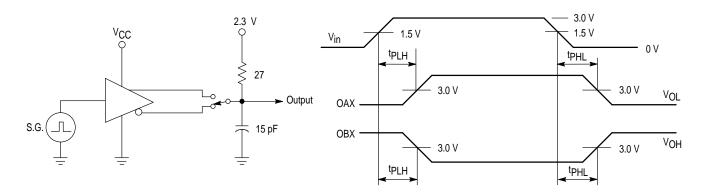

| Propagation Delay – Input to Single Ended Output<br>Input to Output – Low–to–High<br>Input to Output – High–to–Low                                                                                                 | <sup>t</sup> PLH<br><sup>t</sup> PHD                                                                                 | -<br>-           | 10<br>11             | 20<br>20                               | ns   |

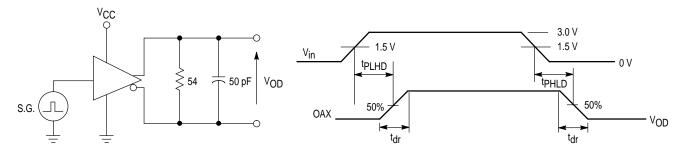

| Propagation Delay – Input to Differential Output<br>Input Low–to–High<br>Input High–to–Low                                                                                                                         | <sup>†</sup> PLHD<br><sup>†</sup> PHLD                                                                               | -<br>-           | 15<br>15             | 23<br>23                               | ns   |

| Differential Output Transition Time                                                                                                                                                                                | t <sub>DR</sub> , t <sub>DF</sub>                                                                                    | _                | 9.0                  | 10.7                                   | ns   |

| Skew Timing MC34058   tplhd - tphld for Each Driver  Maximum - Minimum tplhd Within a Package  Maximum - Minimum tphld Within a Package                                                                            | <sup>t</sup> SK1<br>tSK2<br>tSK3                                                                                     | 0<br>0<br>0      | 0.1<br>_<br>_        | -<br>8.0<br>6.0                        | ns   |

| Skew Timing MC34059   tplhd - tphld  for Each Driver  Propagation Delay Difference Between Any Two Drivers (Same Package or Different Packages at Same V <sub>CC</sub> and T <sub>A</sub> )                        | tSK7<br>tSK8                                                                                                         | 0<br>-           | 0.1<br><4.0          | -<br>-                                 | ns   |

| Enable Timing Single Ended Outputs Enable to Active High Output Enable to Active Low Output Active High to Disable Active Low to Disable Differential Outputs Enable to Active Output Enable to Three—State Output | <sup>†</sup> PZH<br><sup>†</sup> PZL<br><sup>†</sup> PHZ<br><sup>†</sup> PLZ<br><sup>†</sup> PZD<br><sup>†</sup> PDZ | -<br>-<br>-<br>- | 15<br>25<br>12<br>10 | 40<br>40<br>25<br>25<br>25<br>40<br>25 | ns   |

| TIMING CHARACTERISTICS – RECEIVER                                                                                                                                                                                  | 1 02                                                                                                                 | 1                | 1                    |                                        | 1    |

| Propagation Delay Input to Output – Low–to–High Input to Output – High–to–Low                                                                                                                                      | <sup>t</sup> PLHR<br><sup>t</sup> PHLR                                                                               | <u>-</u>         | 16<br>16             | 23<br>23                               | ns   |

| Skew Timing  tpLHR - tpHLR  for Each Receiver   Maximum - Minimum tpLHR Within a Package   Maximum - Minimum tpHLR Within a Package                                                                                | <sup>†</sup> SK4<br><sup>†</sup> SK5<br><sup>†</sup> SK6                                                             | 0<br>0<br>0      | 1.0<br>_<br>_        | -<br>3.0<br>3.0                        | ns   |

| Skew Timing Propagation Delay Difference Between Any Two Receivers in Different Packages at Same V <sub>CC</sub> and T <sub>A</sub> (MC34059 Only)                                                                 | <sup>t</sup> SK9                                                                                                     | _                | <5.0                 | _                                      | ns   |

| Enable Timing Single Ended Outputs Enable to Active High Output Enable to Active Low Output Active High to Disable Active Low to Disable                                                                           | <sup>‡</sup> PZHR<br><sup>‡</sup> PZLR<br><sup>‡</sup> PHZR<br><sup>‡</sup> PLZR                                     | -<br>-<br>-      | 15<br>25<br>12<br>10 | 22<br>30<br>25<br>25                   | ns   |

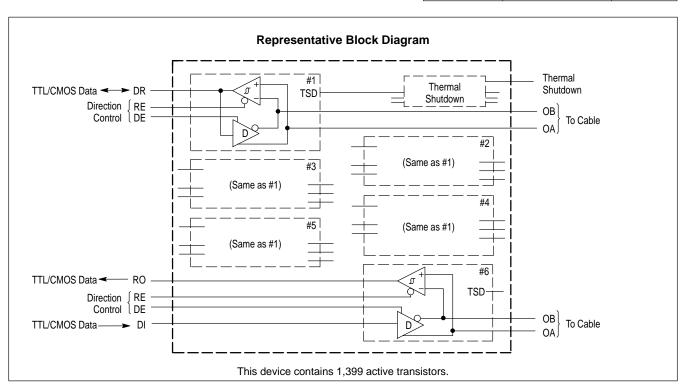

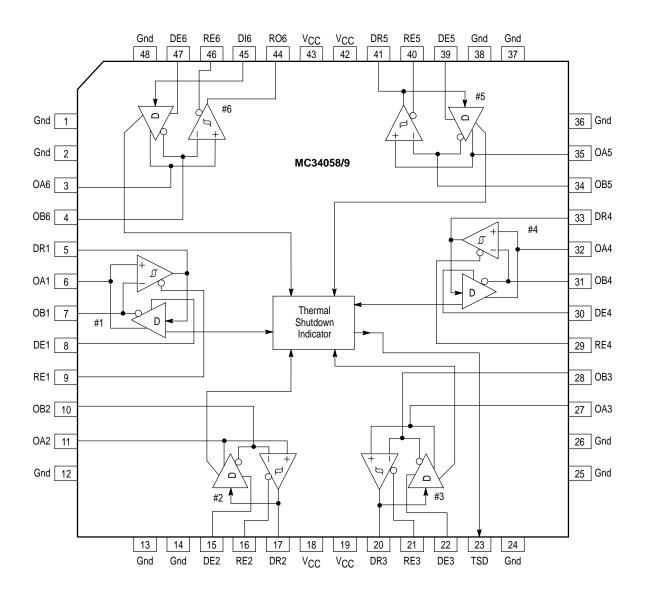

## **Block Diagram and Pinout**

#### **PINOUT SUMMARY**

| OA  | NonInverting Output/Input          | DE  | Driver Enable, Active High (TTL)  |  |

|-----|------------------------------------|-----|-----------------------------------|--|

| ОВ  | OB Inverting Output/Input          |     | Receiver Enable, Active Low (TTL) |  |

| DR  | Driver Input/Receiver Output (TTL) | TSD | Thermal Shutdown Indicator        |  |

| DI6 | #6 Driver Input (TTL)              | Vcc | Connect 4 Pins to 5.0 V, ±10%     |  |

| RO6 | #6 Receiver Output (TTL)           | Gnd | Connect 12 Pins to Circuit Ground |  |

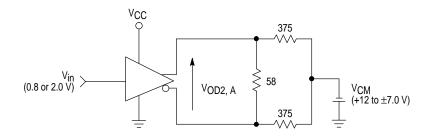

Figure 1.  $V_{\mbox{\scriptsize OD}}$  and  $V_{\mbox{\scriptsize OS}}$  Test Circuit

Figure 2.  $V_{\mbox{OD}}$  and  $V_{\mbox{CM}}$  Test Circuit

Figure 3. VOD AC Test Conditions

Figure 4. VOH and VOL AC Test Conditions

Figure 5. V<sub>OH</sub> versus I<sub>OH</sub>

4.6

4.4

4.2

4.0

3.8

3.6

-80

-60

-40

-20

0

I<sub>OH</sub> (mA)

#### Description

The MC34058/9 is a differential line driver designed to comply with EIA–485 Standard for use in balanced digital multipoint systems containing multiple drivers. The drivers also comply with EIA–422–A and CCITT Recommendations V.11 and X.27. Positive and negative current limiting of the drivers meet the EIA–485 requirement for protection from damage in the event that two or more drivers try to transmit simultaneously on the same cable. Data rates in excess of 10 MBPS are possible, depending on the cable length and cable characteristics. Only a single power supply, 5.0 V  $\pm 10\%$  is required.

#### **Driver Inputs**

The driver inputs and enable logic determine the state of the outputs in accordance with Table 1. The driver inputs have a nominal threshold of 1.2 V, and the voltage must be kept within the range of 0 V to  $V_{CC}$  for proper operation. If the voltage is taken more than 0.5 V below ground or above  $V_{CC}$ , excessive currents will flow and proper operation of the drivers will be affected. An open Pin is equivalent to a logic high, but good design practices dictate that inputs should never be left open. The inputs are TTL type and their characteristics are unchanged by the state of the enable pins.

#### **Driver Outputs**

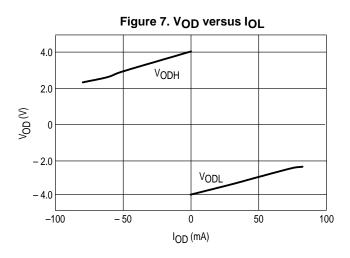

Each output (when active) will be a low or a high voltage, depending on the input state and the load current (see Tables 1, 2 and Figures 2 and 3). The graphs apply to each driver, regardless of how many other drivers within the package are supplying load current.

Table 1. Driver Truth Table

|                    | Enables |     | Outputs     |             |

|--------------------|---------|-----|-------------|-------------|

| Driver Data Inputs | DEX     | REX | OAX         | ОВХ         |

| Н                  | Н       | Н   | Н           | L           |

| L                  | Н       | Н   | L           | Н           |

| X                  | L       | Н   | Z           | Z           |

| X                  | Н       | L   | Not Defined | Not Defined |

The outputs will be in a high impedance state when:

- a) The Enable inputs are set according to Table 1;

- b) The junction temperature exceeds the trip point of the thermal shutdown circuit. When in this condition, the output's source and sink capability are shut off, and a leakage current of less than 20 μA will flow. Disabled outputs may be taken to any voltage between –7.0 V and 12 V without damage to internal circuitry.

The drivers are protected from short circuits by two methods:

- a) Current limiting is provided at each output, in both the source and sink direction, for shorts to any voltage within the 12 V to -7.0 V range, with respect to circuit ground. The short circuit current will flow until the fault is removed, or until the thermal shutdown activates. The current limiting circuit has a negative temperature coefficient and requires no resetting upon removal of the fault condition.

- b) A thermal shutdown circuit disables the outputs when the junction temperature reaches +150°C, ± 20°C. The thermal shutdown circuit has a hysteresis of ~ 12°C to prevent oscillations. When this circuit activates, the output stage of each driver is put into the high impedance mode, thereby shutting off the output currents. However, the remainder of the internal circuitry remains biased and the outputs will become active once again as the IC cools down.

#### **Receiver Inputs**

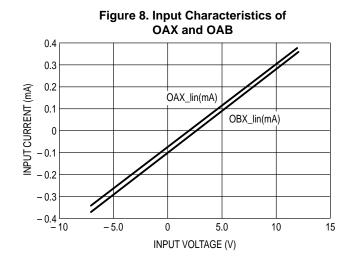

The receiver inputs and enable logic determine the state of the receiver outputs in accordance with Table 2. Each receiver input pair has a nominal differential threshold of at most 200 mV (Pin OAX with respect to OBX) and a common mode voltage range of –7.0 V and 12 V must be maintained for proper operation. A nominal hysteresis of 100 mV is typical. The receiver input characteristics are shown in Figure 8. When the inputs are in the high impedance state, they remain capable of the common mode voltage range of –7.0 V to 12 V.

#### **Receiver Outputs**

The receiver outputs are TTL type outputs and act in accordance with Table 2.

#### **Enable Logic**

Each driver output is active when the Driver Enable input is true according to Table 1. Each receiver output is active when the Receiver Enable input is true according to Table 2.

The Enable inputs have a nominal threshold of 1.2 V and their voltage must be kept within the range of 0 V and V<sub>CC</sub> for proper operation. If the voltage is taken more than 0.5 V below ground or above V<sub>CC</sub>, excessive currents will flow and proper operation of the drivers will be affected. An open pin is equivalent to a logic high, but good design practices dictate that inputs should never be left open. The enable inputs are TTL compatible. Since the same pins are used for driver input and receiver output, care must be taken to make sure that DEX and REX are not both enabled. This may result in corruption of both the transmitted and received data.

Table 2. Receiver Truth Table

| Receiver Data Inputs | Ena | Outputs |             |

|----------------------|-----|---------|-------------|

| OAX-OBX              | DEX | REX     | DRX         |

| ≥ + 200 mV           | L   | L       | Н           |

| ≤-200 mV             | L   | L       | L           |

| X                    | L   | Н       | Z           |

| X                    | н   | L       | Not Defined |

#### **APPLICATIONS**

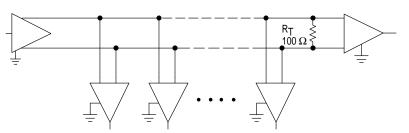

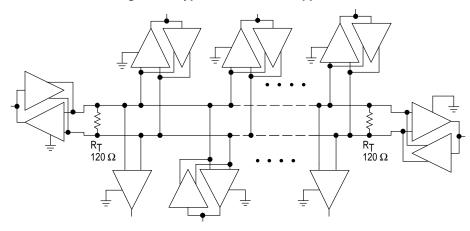

The MC34058/9 was designed to meet EIA/TIA-422 and EIA/TIA-485 standards. EIA/TIA-422 specifies balanced point-to-point transmission with the provision for multiple receivers on the line. EIA/TIA-485 specifies balanced

point-to-point transmission and allows for multiple drivers and receivers on the line. Refer to EIA/TIA documents for more details. Figure 9 shows a typical EIA/TIA-422 example. Figure 10 shows a typical EIA/TIA-485 example.

Figure 9. Typical EIA/TIA-422 Application

Figure 10. Typical EIA/TIA-485 Application

EIA/TIA–422 specifications require the ability to drive at least 10 receivers of input impedance of greater than or equal to 4.0 K $\Omega$  plus the 100  $\Omega$  termination resistor. This protocol was intended for unidirectional transmission. EIA/TIA–485 is capable of bidirectional transmission by allowing multiple drivers and receivers on the same twisted pair segment. The loading of the twisted pair segment can be up to 32 Unit Loads (U.L.) plus the two 120  $\Omega$  terminating resistors. The U.L. definition is shown in Figure 11.

Figure 11. TIA/EIA-485 Unit Load Definition

# Calculating Power Dissipation for the MC34058/9 Hex-Transceiver.

The operational temperature range is listed as 0°C to 70°C to satisfy both EIA/TIA–485 and EIA/TIA–422 specifications. However, a lower ambient temperature may be required depending on the specific board layout and/or application.

Using a first order approximation for heat transfer, the maximum power which may be dissipated by the package is determined by (see Appendix A for more details);

$$P_{Dmax} = \frac{T_{Jmax} - T_{A}}{\theta ja}$$

[1]

where:

$\theta ja$  = package thermal resistance (see Appendix A)  $T_{Jmax}$  = Maximum Junction Temperature. Since the thermal shutdown feature has a trip point of 150°C  $\pm$  20°,  $T_{Jmax}$  is selected to be +130°C.

$T_A$  = Ambient Operating Temperature.

The power generated within the package is then;

$$PD = \left\{ \left[ \left( V_{CC} - V_{OH_1} \right) \cdot I_{OH_1} \right] + V_{OL_1} \cdot I_{OL_1} \right\} + \dots$$

$$(\text{each\_driver}).. + \left\{ \left[ \left( \text{V}_{\text{CC}} - \text{V}_{\text{OH}_6} \right) \cdot \text{I}_{\text{OH}_6} \right] + \right.$$

$$V_{OL_6} \cdot I_{OL_6}$$

+  $V_{CC} \cdot I_{CCQ}$  [2]

As indicated in the equation, the part of Equation 2 consisting of  $I_{OH}$ ,  $V_{OH}$ ,  $I_{OL}$  and  $V_{OL}$  must be calculated for each of the drivers and summed for the total power dissipation estimate. The last term can be considered the quiescent power required to keep the IC operational and is measured with the drivers idle and unloaded. The  $V_{OH}$  and  $V_{OL}$  terms can be determined from the output current versus output voltage curves which provide driver output characteristics.

Example 1 estimates thermal performance based on current requirements.

#### **Example 1. Balanced and Unbalanced Operation**

$I_{OL}$  = 50 mA and  $I_{OH}$  = ±50 mA for each driver.  $V_{CC}$  = 5.0 V.

How many drivers can be used? (Typical power supply current  $I_{CCO} = 18 \text{ mA.}$ )

$$I_{CCQ} = 0.018 A$$

The quiescent power is given by:  $PQ = I_{CCQ} \cdot V_{CC}$ , and is equal to PQ = 0.09 W.

#### **Balanced Operation:**

To determine the amount of power dissipated by each output stage we need to know the differential output voltage for the output current required. Figure 7 shows that for IOH and IOL differential of 50 mA, VODH and VODL are:

$$V_{OD} = |3.0|$$

, and  $I_{OL} = |I_{OH}| = I_{Out} = 0.050$  A.

And the power dissipated by each driver is given by;

$$P_{DrvB} = I_{Out} \cdot (V_{CC} - V_{OD})$$

and equal to  $P_{DrvB} = 0.10 \text{ W}.$

#### **Unbalanced Operation:**

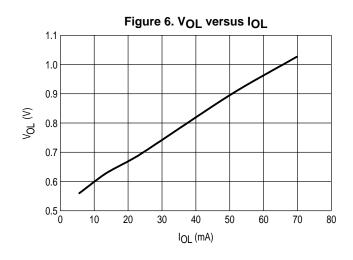

To determine the amount of power dissipated by each output stage we need to know the single-ended output voltage for the output current required. Figures 5 and 6 shows that for an IOH and IOL of ±50 mA,

$$V_{OH} = 3.9 \text{ V} \quad V_{OL} = 0.895 \text{ V}$$

And the power dissipated by each driver is calcu-

$$P_{DrVU} = (V_{CC} - V_{OH}) \cdot |I_{OH}| + V_{OL} \cdot I_{OL}$$

and equal to

$P_{DrylJ} = 0.10 W.$

(For this example, balanced operation is assumed.)

Summing the quiescent and driver power for 6 transceivers operating in a package produces;

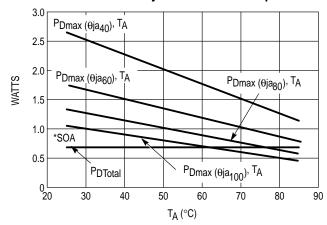

For the MC34058/9, the thermal resistance is capable of a wide range. The ability of the package to dissipate power depends on board type and temperature, layout and ambient temperature (see Appendix A). For the purposes of this example the thermal resistance can range from 40°C/W to 100°C/W;

$$\theta$$

ja = j, j = 40, 60, .. 100°C/W.

Varying the ambient operating temperature TA = 25, 30, .. 85°C; specifying a maximum junction temperature to avoid thermal shutdown T<sub>.lmax</sub> = 130°C; and using the first order approximation for maximum power dissipation;

$$P_{Dmax(\theta ja)}$$

,  $T_A = \frac{T_{Jmax} - T_A}{\theta ja}$

produces a set curves that can be used to determine a Safe Operating Area for the specific application. PDTotal is graphed with P<sub>Dmax</sub> to provide a reference.

# **Graph of Maximum Power Dissipation Possible** for a Particular θja and Ambient Temperature

<sup>\*</sup> Safe Operating Area (SOA), is an operating power, PDTotal, less than PDmax.

So all the drivers in the package can be used if the thermal resistance and/or the ambient temperature is low enough.

#### Appendix A. Optimizing the Thermal Performance of the MC34058/9

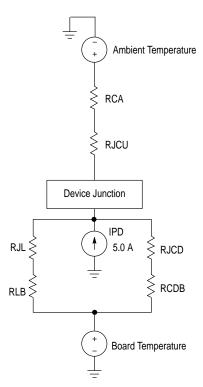

Figure 12. Electrical Model of Package Heat Transfer

An equivalent electrical circuit for the thermal model for the MC34058/9 package is shown in Figure 12. It is a simplified model that shows the dominant means of heat transfer from the thermally enhanced 48–ld package used for the MC34058/9. The model is a first order approximation and is intended to emphasize the need to consider thermal issues when designing the IC into any system. It is however customary to use similar models and Equation 1 to estimate device junction temperatures.

Equation 1 is the common means of using the thermal resistance of a package to estimate junction temperature in a particular system.

$$T_{J} = (P_{D} \cdot \theta j x) + T_{A}$$

[1]

The term  $\theta jx$  in Equation 1 is usually quoted as a øja value in °C/Watt. However, since the 48–ld package for the MC34058/9 has been thermally enhanced to take advantage of other heat sinking potentials, it must be modified.  $\theta jx$  must actually be considered a composite of all the heat transfer paths from the chip. That is, the three dominant and parallel paths shown in Figure 12. Of those three paths, potentially the most effective is the corner package leads. This is because these corner leads have been attached to the flag on which the silicon die is situated. These pins can be connected to circuit board ground to provide a more efficient conduction path for internal package heat. This path is modeled as the RjI (junction–to–leads) and RIb

(leads-to-board) combination in Figure 12. This path provides the most effective way of removing heat from the device provided that there is a viable temperature potential (i.e. heat sinking source) to conduct towards. However, if it is not properly considered in the system design, the other paths, (Rjcd + Rcdb) and (Rjcu + Rca) attain greater importance and must be more carefully considered.

So Equation 1, modified to reflect a more complete heat transfer model becomes:

$$T_{J} = T_{A} \cdot \frac{\left(\frac{1}{\frac{1}{Rjcd} + \frac{1}{Rjlb}}\right)}{\left(\frac{1}{\frac{1}{Rjcd} + \frac{1}{Rjlb}}\right) + Rjca} + \dots$$

[2]

...

$$T_B \cdot \frac{Rjca}{\left(\frac{1}{Rjcd} + \frac{1}{Rjlb}\right) + Rjca} + PDISS \cdot \theta ja$$

where;

T<sub>J</sub>= Junction Temperature

T<sub>A</sub> = Ambient Temperature

T<sub>B</sub> = Board Temperature

PDISS = Device Power

and  $\theta$ ja = Total Thermal Resistance and is composed the parallel combination of all the heat transfer paths from the package.

While Equation 2 is still only a first order approximation of the heat transfer paths of the MC34058/9, at least now it includes consideration for the most effective heat transfer path for the MC34058/9; the board to which the device is soldered. The modified equation also better serves to explain how external variables, namely the board and ambient temperatures, affect the thermal performance of the MC34058/9.

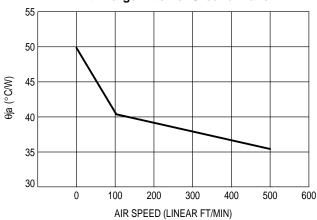

Methods of removing heat via the flag connected pins can be classified into two means; conduction and convection. Radiation is omitted as the contribution is small compared to the other means. Conduction is by far the best method to draw heat away from the MC34058/9 package. This is best accomplished by using a multilayer board with generous ground plane. In this case, the flag connected pins can be connected directly to the ground plane to maximize the heat transfer from the package. Figure 13 shows the results of thermal measurements of a board with an external ground plane (the actual ground area was approximately 6 1/4 in<sup>2</sup>). The thermal leads are connected to the board ground plane per the recommended strategy.

Figure 13. Thermal Resistance (θja) for Board with Large External Ground Plane

$\theta jc$  for the package on this board is  $25\pm20\%$  depending on the location of the package on the board.

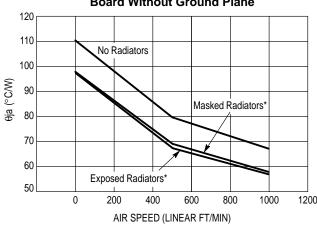

Figure 14A. Thermal Resistance (θja) for Board Without Ground Plane

\* Masked radiators were covered by a solder mask. Exposed radiators were bare copper.

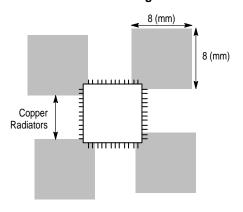

Figure 14B. Layout Used for Thermal Resistance

Measurements in Figure 14A

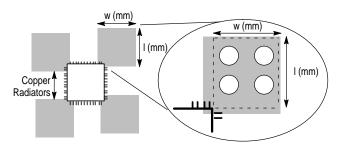

Figure 15. Placement of Thermal Vias to Enhance Heat Transfer to Ground Plane

Figure 14A on the other hand shows the result of a single layer board without an internal ground plane. The graphs show that even though there are radiators of substantial area surrounding the package, substantial degredation of thermal performance is evident (Figure 14B shows the layout used for the measurements in Figure 14A). Comparing Figures 13 and 14A shows almost a 2:1 improvement for the strategy involving the external ground plane.

It is clear from Figures 13, 14A and Example 1, that if an application is to use all the device drivers, preparations to assure adequate thermal performance of the system must be taken.

If an extensive external ground plane is unavailable, and only an internal ground plane is available, the thermal performance of the device can still be improved by providing thermal vias to connect the radiators to the internal ground plane. Figure 15 shows a proposed scheme for thermal vias (contact board manufactures for specifics about the thermal performance of their products and possible enhancements).

The thermal resistance for this structure on 1.0 oz. Copper connecting each of the four radiators to an internal ground plane and provide an estimated thermal resistance of approximately 5.0°C/W. The vias used in the estimate had 80 mil diameters, on 100 mil centers and a 1.0 mil copper thickness.

H o w t o r e a c h

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution;

P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454

u n

MFAX: RMFAX0@email.sps.mot.com - TOUCHTONE 602-244-6609 INTERNET: http://Design-NET.com

JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

m

а

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298

0

0

С